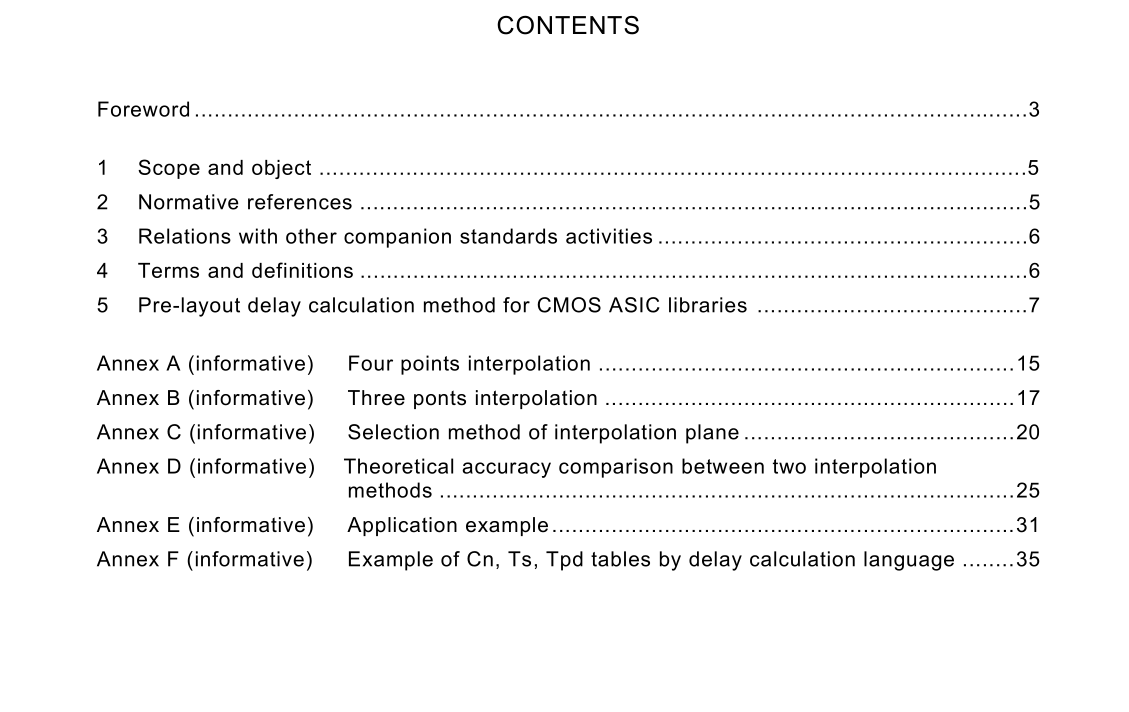

IEC 61523-2 pdf download

IEC 61523-2 pdf download.Delay and power calculation standards

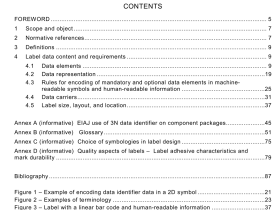

1. Scope and object

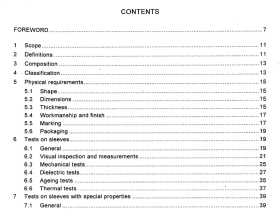

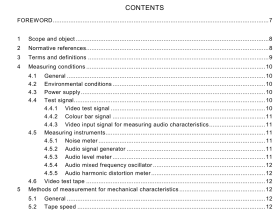

This standard specifies the pre-layout delay calculation method for CMOS1 “ASIC2) Libraries which contains cell based primitives and memories to be used during the pre-layout design phase of Logic simulation, Timing verification, and Logic synthesis. The delay calculation method addressed in this standard consists of 1) Estimation of wire capacitance and 2) Delay calculation method based on tablelook-up. With use of DCL and SDF, this delay calculation method helps the user have a unified timing model for various EDA tools in the pre-layout design phase. This standard is consistent with existing standards and accepts existing standard formats, like SPEF, DCL, and SDF. Scope of this standard covers the CMOS ASIC front end timing design for using logic synthesizer, simulators, timing verifiers. The delay calculation method specified is based on the input slew rate calculation step and the port to port calculation step. During these calculation steps, the table lookup method is used. The table method of this standard specifies two interpolation methods for delay calculation. One is bi-linear interpolation which is widely used through the industry. Another is a linear interpolation using neighboring 3 points. The nature of the delay value has monotonously increasing function of convex surface. This linear interpolation has a few percent of differences between linear interpolation and SPICE result.

3. Relations with other companion standards activities

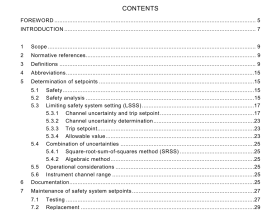

The input to the delay calculator are net list and library. The net list is described on either Verilog or VHDL. The library consists of a functional part and a delay parameter part. The functional part of the library is covered by Verilog or VHDL. NOTE The delay parameter part of the library has not been standardized, because it depends strongly on the delay calculation method. EIAJ/ALR version1.1 described the delay calculation method , and the delay calculation method of EIAJ/ALR version1.1 is represented by DCL and DCL-PI standard(IEEE 1481). This part of IEC 61523 specifies in detail a table look up calculation formula for CMOS ASIC library). The output of the delay calculator is a Standard Delay Format (SDF).

5.2. Table Look-Up delay calculation method The table look-up model of delay calculation specification uses 3 types of table models. First is the ‘Net capacitance table’ (named Cn table). This table is used for ‘load capacitance’ estimation. Second is ‘Input slew rate table’ (named Ts table), and 3rd is ‘Port to port propagation delay time table’ (named Tpd table). As a first step of delay calculation, input slew rate is calculated by using net capacitance, and Ts table. And then, port to port propagation delay can be calculated by using net capacitance, input slew rate, and Tpd table. The propagation delay is calculated using a Tpd table by applying one of the methods for interpolation approximation. One is bilinear interpolation approximation by 4 points. This method will be de facto standard from major EDA vendors. The other is linear interpolation approximation by 3 points. This approximation is more accurate than bilinear interpolation, and both linear and bilinear methods can use the same Tpd table. 5.2.1 Load capacitance estimation First step is to estimate the load capacitance of each net. Load capacitance is estimated by the following rule.

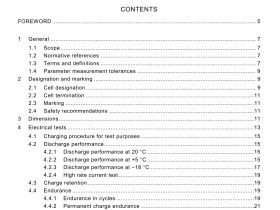

4. Terms and Definitions

capacitance of the net: Net means equipotential signal pins which will be connected by routing. The capacitance of the net is the capacitance of all the signal pins tha tare connected by routing. CMOS: Complementary Metal Oxide Semiconductor. DCL: Delay Calculation Language. front end design: Logical design phase of ASIC design. Back end design means layout design. gate: module containing only one output which is a simple boolean function of its inputs. Some basic simple boolean functions are and/or/not. input slew rate: Slope of the input signal of the gate.In CMOS,the gate output delay is the function of its input slope of the signal. load capacitance: Capacitance driven by gate. Usually it is separated into two items: i.e. wiring load capacitance and the sum of input load capacitance. logic synthesizer: CAD package function performing the trans lation from RTL-level descriptions to Gat-level descriptions. port to port delay: One meaning is pin to pin delay inside of gate. The other is pin to pin delay between gates. pre-layout: Design phase before layout, i.e.logical design phase.